인텔, 맞춤형 트랜지스터 '터보 셀' 기술 공개

Master

0

0

0

0

3시간전

Master

0

0

0

0

3시간전

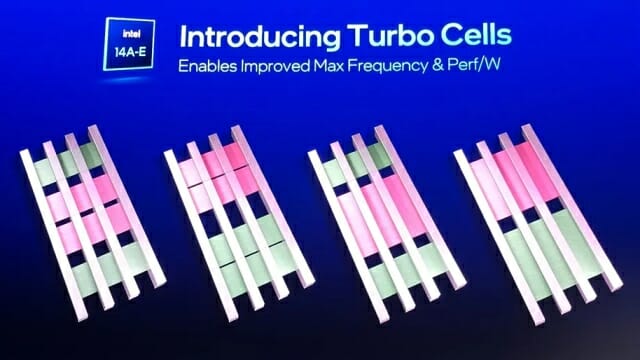

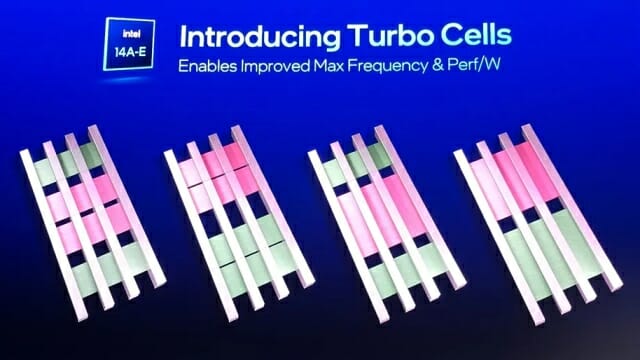

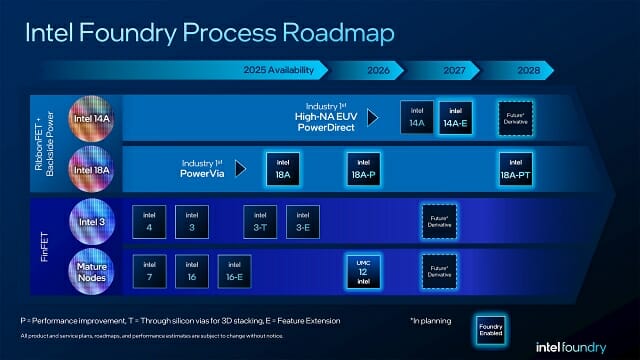

인텔이 29일(현지시간) 오는 2027년부터 리스크 생산에 들어갈 1.4나노급 미세공정 '인텔 14A'(Intel 14A)에 도입될 새로운 트랜지스터 적층 구조 '터보 셀'(Turbo Cell)을 투입할 예정이다.

인텔 14A 공정은 2세대 반도체 후면 전력 전달 기술(BSPDN)인 '파워다이렉트'를 이용해 인텔 18A 대비 와트 당 성능을 최대 20% 향상시키고 같은 면적에 넣을 수 있는 트랜지스터 수를 최대 1.3배 높였다.

30일 미국 IT 매체 톰스하드웨어에 따르면, 인텔은 미국 캘리포니아 주 새너제이에서 진행한 '인텔 파운드리 다이렉트 커넥트 2025' 행사에서 전력 소모와 성능을 최소화할 수 있는 새로운 트랜지스터 구조인 '터보 셀'을 공개했다.

인텔 14A 공정은 반도체 설계시 ▲ 고주파수 작동에 최적화됐지만 전력 소모가 큰 '톨'(Tall), ▲ 와트 당 성능에 최적화된 '중간'(mid-size), ▲ 면적과 전력 소모를 줄인 '숏'(Short) 등 전자설계자동화(EDA) 소프트웨어에서 활용할 수 있는 셀 라이브러리를 3개 제공한다.

이 중 숏 라이브러리는 전력 소모 최적화와 트랜지스터 수 확보가 필요한 CPU와 GPU 설계에 주로 활용된다. 인텔은 숏 라이브러리에 터보 셀을 투입해 전력 소모와 성능 최적화를 구현할 예정이다.

터보셀 기술은 반도체 안에서 성능이 중요한 부분에는 고성능 트랜지스터를, 전력 소모를 줄여야 하는 트랜지스터에는 고효율 트랜지스터를 배치하는 맞춤형 설계가 가능하다.

이를 통해 CPU와 GPU의 작동 성능은 높이면서 전력 소모와 발열은 최소화한 설게를 구현할 수 있다. 반도체 성능 평가에 흔히 쓰이는 지표인 전력·성능·면적(PPA)의 균형을 찾아 같은 트랜지스터 수에서 더 우수한 제품을 만들 수 있다.

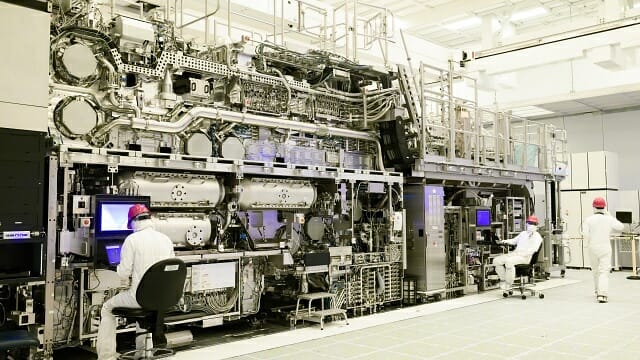

인텔은 인텔 14A 공정의 파생 공정인 '인텔 14A-E'에 터보 셀을 적용할 예정이다. 공정 뒤에 붙은 알파벳 'E'는 '기능 확장'을 의미한다. 인텔은 인텔 14A 공정의 PPA를 향상시키기 위해 고개구율(High-NA) 극자외선(EUV) 공정 활용도 검토하고 있다.

지난 29일 '인텔 파운드리 다이렉트 커넥트 2025' 기조연설에서 나가 찬드라세카란 인텔 COO는 "인텔 14A 공정에 기존 EUV나 고개구율 EUV 기술 중 어느 쪽이나 활용할 수 있으며 적절한 시점에 활용을 검토 중"이라고 말했다.